Studiul decodificatoarelor şi

multiplexoarelor (folosind

programul Digital Works)

1.

Consideraţii teoretice

Într-un sistem digital se folosesc diverse coduri,

altele decât cel binar natural pentru codarea informaţiei. Folosirea

decodificatoarelor este absolut necesarã pentru a putea trece de la o

reprezentare la alta. Ele sunt circuite combinaţionale realizate cu

porţi logice.

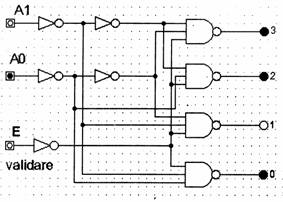

Vom exemplifica funcţionarea unui

decodificator cu ajutorul unui circuit numit decodor 1 din 4. Denumirea sa

furnizeazã şi detalii despre modul de funcţionare: în funcţie de

codul de la intrãrile de adrese A0

şi A1, una dintre

cele patru ieşiri este în zero logic; tabela de adevãr pentru un astfel de

circuit este cea datã în figura 1. Tot în aceastã figurã este prezentatã schema unui astfel de

decodificator, simulatã în Digital Works.

|

Intrări |

Ieşiri |

|||||

|

E |

A1 |

A0 |

0 |

1 |

2 |

3 |

|

1 |

X |

X |

1 |

1 |

1 |

1 |

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

0 |

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

0 |

Fig.1

Din tabel se poate observa cu uşurinţã

cã, funcţie de biţii de la intrãrile A0 şi A1,

una dintre ieşiri şi anume cea datã de numãrul zecimal A1×21 + A0×20 va fi în 0 logic. În cazul

circuitului simulat din figura 1, ieşirea notatã 1 este în 0 logic. Borna E,

numitã bornã de validare (Enable -

în limba englezã) inhibã ieşirile circuitului atunci când este în 1 logic;

prima linie a tabelului din figura 1 pune în evidenţã acest mod de

funcţionare: semnul X de la cele douã intrãri A aratã cã ele nu

influenţeazã în nici un fel funcţionarea circuitului.

Existã şi alte tipuri de decodificatoare: 1

din 8, BCD - zecimal (1 din 10), BCD - 7 segmente, ş.a. Unele dintre ele

sunt realizate sub forma unor circuite integrate dedicate, altele se pot

implementa utilizând porţi logice şi/sau alte decodificatoare.

Vom exemplifica funcţionarea unui alt

decodificator, numit decodor BCD - 7 segmente, folosit pentru comanda

dispozitivelor de afişare cu led-uri cu şapte segmente. Fiecãrui

segment i s-a atribuit o denumire, aşa cum se aratã în figura 2.a.

(a)

|

0 |

0 |

0 |

0 |

0 |

abcdef |

8 |

1 |

0 |

0 |

0 |

abcdefg |

|

1 |

0 |

0 |

0 |

1 |

bc |

9 |

1 |

0 |

0 |

1 |

abcdfg |

|

2 |

0 |

0 |

1 |

0 |

abged |

10 |

1 |

0 |

1 |

0 |

deg |

|

3 |

0 |

0 |

1 |

1 |

abcdg |

11 |

1 |

0 |

1 |

1 |

cdg |

|

4 |

0 |

1 |

0 |

0 |

bcfg |

12 |

1 |

1 |

0 |

0 |

bfg |

|

5 |

0 |

1 |

0 |

1 |

acdfg |

13 |

1 |

1 |

0 |

1 |

adfg |

|

6 |

0 |

1 |

1 |

0 |

acdefg |

14 |

1 |

1 |

1 |

0 |

cdfg |

|

7 |

0 |

1 |

1 |

1 |

abc |

15 |

1 |

1 |

1 |

1 |

- |

(b)

Fig.2

Evident, pentru a afişa o cifrã, trebuie

comandate doar anumite segmente: de exemplu pentru cifra 6 trebuie sã existe

semnal de comandã pentru segmentele a, c, d, e, f, şi g. Totodatã cifra zecimalã şase

este reprezentatã în cod binar de numãrul 0110; în consecinţã, decodorul

va activa ieşirile a, c, d, e, f,

şi g atunci când cuvântul de la intrare este 0110. În tabelul din

figura 2.b se dau codurile binare şi segmentele comandate pentru fiecare cuvânt

de patru biţi. Deoarece sunt patru biţi, existã 24 stãri

posibile şi din acest motiv în afara cifrelor propriu-zise apar şi

alte combinaţii ale segmentelor. Acestea sunt decodificate în funcţie

de aplicaţia specificã a fiecãrui decodor. În unele cazuri ele reprezintã

cifrele urmãtoare în sistemul de numeraţie hexazecimal.

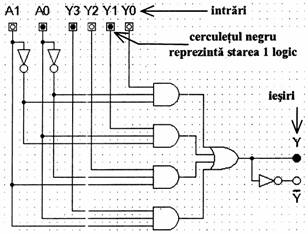

Multiplexoarele sunt circuite logice care permit

transferul informaţiei la o ieşire de la una din cele 2n intrãri, funcţie de

selecţia realizatã cu n

biţi de adresã. Vom exemplifica funcţionarea unui multiplexor cu

ajutorul schemei din Fig.3, care simuleazã schema

logicã a unui multiplexor cu patru cãi.

Fig.3

Cei doi

biţi, A0 şi A1, selecteazã una dintre

intrãri iar bitul prezent la aceastã intrare este transferat la ieşirea Y. Intrãrile A se mai numesc intrãri de adrese sau, pe scurt,

adrese, iar cele Yi -

intrãri de date. Pentru cazul concret din figura 3 se poate observa faptul cã A0=1 şi A1=0 şi în

consecinţã bitul 1 prezent la intrarea corespunzãtoare codului binar A1A0=01 (Y1) este transferat la

ieşire, indiferent de stãrile celorlalte intrãri. Acest lucru poate fi

urmãrit şi în tabela de adevãr din Fig. 4, unde cu X s-au notat biţii

a cãror valoare este indiferentã. Ecuaţia de funcţionare a

multiplexorului prezentat este urmãtoarea:

Y=(Y0.A0'.A1'+Y1.A0'.A1+Y2.A0.A1'+Y3.A0.A1)

|

A0 |

A1 |

Y0 |

Y1 |

Y2 |

Y3 |

Y |

|

X |

X |

X |

X |

X |

X |

0 |

|

0 |

0 |

0 |

X |

X |

X |

0 |

|

0 |

0 |

1 |

X |

X |

X |

1 |

|

0 |

1 |

X |

0 |

X |

X |

0 |

|

0 |

1 |

X |

1 |

X |

X |

1 |

|

1 |

0 |

X |

X |

0 |

X |

0 |

|

1 |

0 |

X |

X |

1 |

X |

1 |

|

1 |

1 |

X |

X |

X |

0 |

0 |

|

1 |

1 |

X |

X |

X |

1 |

1 |

Fig.4

Se

poate observa cã un asemenea dispozitiv poate genera orice funcţie logicã

de trei variabile.

Multiplexoarele se

realizeazã în variante constructive cu 4, 8, 10 sau 16 intrãri de date.

Variantele realizate în

tehnologie CMOS ale multiplexoarelor funcţioneazã dupã acelaşi

principiu, însã au în plus o facilitate importantã: permit multiplexarea

semnalelor analogice, deoarece tranzistorii MOS se comportã ca veritabile

comutatoare. Un avantaj în plus îl constituie şi faptul cã transferul

semnalelor este permis în ambele sensuri.

2.

Procedeul experimental

a) Se verificã

funcţionarea unui decodificator 1 din 8 astfel:

·

se încarcã fişierul 1din8.dwm (se face clic pe butonul 1, urmat de dublu clic

pe numele fişierului);

·

se apasã 4pentru a începe simularea;

·

se selecteaza I pentru cursor în vederea modificãrii intrãrilor interactive;

·

se cautã combinaţia de

la intrãrile E1, E2 şi E3 care face posibilã

funcţionarea normalã a circuitului;

·

pentru aceastã

configuraţie se modificã intrãrile de adrese, astfel încât sã se

obţinã toate combinaţiile posibile;

·

@ se noteazã

tabela de adevãr a circuitului.

b) @ Se verificã funcţionarea unui decodificator

1 din 10 folosind algoritmul de mai sus şi fişierul 1din10.dwm şi se noteazã tabela de

adevãr.

c) @ Se stabileşte tabela de adevãr a unui

decodificator BCD - 7 segmente simulând funcţionarea acestuia cu ajutorul

fişierului BCD-7.dwm.

d) Utilizând exemplul din

lucrare, se realizeazã în Digital Works

un multiplexor cu 8 cãi:

·

se poziţioneazã opt

porţi SI cu câte patru intrãri

una sub cealaltã;

·

ieşirile acestor

porţi se leagã, folosind unealta pentru legãturi !, la cele patru intrãri de la douã porţi SAU;

· ieşirile porţilor SAU se leagã la rândul lor la cele douã intrãri ale unei alte

porţi SAU; ieşirea

acesteia din urmã va fi ieşirea multiplexorului;

· se poziţioneazã

trei intrãri interactive ![]() pentru cele trei intrãri de adresã şi altele opt

pentru intrãrile de date;

pentru cele trei intrãri de adresã şi altele opt

pentru intrãrile de date;

· legãturile de la intrãrile de date

şi de la cele de adrese, la fiecare dintre porţile SI cu patru intrãri, se fac dupã

urmãtoarea regulã: se conecteazã la Ai

intrarea porţii a cãrei adresã scrisã în binar are 1 logic pe acea

poziţie; în caz contrar legãtura se face la ![]() ; de asemenea una dintre intrãrile

fiecãrei porţi trebuie conectatã la intrarea de date respectivã (pentru

care s-a poziţionat intrarea interactivã);

; de asemenea una dintre intrãrile

fiecãrei porţi trebuie conectatã la intrarea de date respectivã (pentru

care s-a poziţionat intrarea interactivã);

· la ieşirea multiplexorului se leagã un led;

· se poate insera text în zona de lucru

astfel:

·

@ se face simularea şi apoi se

stabileşte tabela de adevãr.

3. Conţinutul referatului

·

Schemele folosite şi

tabelele de adevãr completate pentru fiecare caz în parte.

·

Explicaţi de ce se pot

realiza orice funcţii de trei variabile logice cu ajutorul unui

multiplexor 1 din 8.

·

Ce schimbãri ar trebui fãcute

pentru ca multiplexoarele şi decodificatoarele prezentate sã realizeze

funcţia negatã ?