Digital Circuits Laboratory LAB no. 6.

# **MULTIPLEXERS**

Multiplexers are combinational logic circuits that switch the data from one of its input to a unique output. The input is selected through an address word.

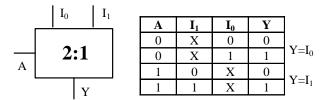

### 1.2 to 1 multiplexer

The circuit allows switching the data from the input  $I_0$  (A=0) or  $I_1$ (A=1) toward the output Y. The circuit symbol and its truth table are presented in figure 1.

The correspondingVK diagram is shown below. By grouping the cells that contain logic 1 we get the equation:

| A I <sub>1</sub> I <sub>0</sub> | 00 | 01         | 11              | 10        |

|---------------------------------|----|------------|-----------------|-----------|

| 0                               | 0  | 0          | $\triangleleft$ | $\square$ |

| 1                               | 0  | $\bigcirc$ | $\square$       | 0         |

$$Y = A \cdot I_0 + A \cdot I_1$$

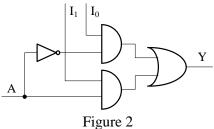

From this equation, the multiplexer will look like in figure 2:

Digital Circuits Laboratory

## LAB no. 6.

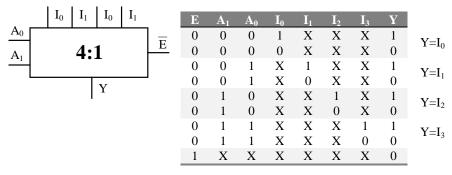

## 2. 4:1 multiplexer with enable input

For addressing 4 inputs, 2 address lines are necessary. Their selection is similar with the one in the address decoder. The circuit has an additional input for enabling its operation.

The circuit symbol and its truth table are presented in figure 3.

| Figura 3 | 3 |

|----------|---|

|----------|---|

The VK diagram associated with this circuit is the following:

| $I_3I_2I_1I_0$ | 0000 | 0001 | 0011 | 0010 | 0110 | 0111 | 0101 | 0100 | 1100 | 1101 | 1111 | 1110 | 1010 | 1011 | 1001 | 1000 |

|----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| $EA_1A_0$      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 000            | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    |

| 001            | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    |

| 011            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| 010            | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    |

| 110            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 111            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 101            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 100            | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

$$Y = \overline{E} \cdot \overline{A_1} \cdot \overline{A_0} \cdot I_0 \cdot (\overline{I_2} \cdot \overline{I_3} + \overline{I_3} \cdot I_2 + I_3 \cdot I_2 + I_3 \cdot \overline{I_2}) + \\ + \overline{E} \cdot \overline{A_1} \cdot A_0 \cdot I_1 \cdot (\overline{I_3} + I_3) + \overline{E} \cdot A_1 \cdot \overline{A_0} \cdot I_2 + \overline{E} \cdot A_1 \cdot A_0 \cdot I_3 = \\ = \overline{E} \cdot (\overline{A_1} \cdot \overline{A_0} \cdot I_0 + \overline{A_1} \cdot A_0 \cdot I_1 + A_1 \cdot \overline{A_0} \cdot I_2 + A_1 \cdot A_0 \cdot I_3)$$

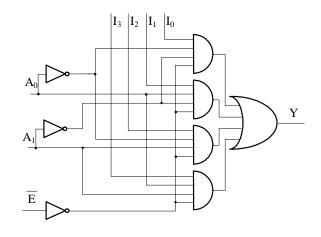

The synthesis needs : - 1 OR gate with 4 inputs

- 4 AND gates with 4 inputs

- 3 inverters

Digital Circuits Laboratory *LAB no. 6*.

### 3. Implementation of logic functions using multiplexers

Any logic function can be written as a sum of miniterms:

$$f = \sum_{i=0}^{2^n - 1} m_i \cdot k_i \tag{1}$$

where: -  $k_i=0$  if the miniterm does not appear in the disjunction

- k<sub>i</sub>=1 if the miniterm appears in the disjunction

The generalized equation of a multiplexer is:

$$Y = \overline{E} \cdot \sum_{i=0}^{2^n - 1} m_i \cdot I_i$$

<sup>(2)</sup>

Comparing the equations (1) and (2) we can conclude that any logic function can be implemented using a multiplexer by connecting the input  $\overline{E}$  to logic 0 and the inputs I<sub>i</sub> to logic 1 respectively to logic 0 if the miniterm appears in function or not.

## **Example:**

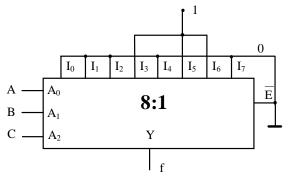

Considering the function  $f = \overline{A} \cdot B \cdot C + A \cdot \overline{B} \cdot C + A \cdot B \cdot \overline{C}$ it can be rewritten:

$$f = \underbrace{A \cdot B \cdot C}_{I_0} \cdot 0 + \underbrace{A \cdot B \cdot C}_{I_1} \cdot 0 + \underbrace{A \cdot B \cdot C}_{I_2} \cdot 0 + \underbrace{A \cdot B \cdot C}_{I_3} + \underbrace{\overline{A \cdot B \cdot C}}_{I_4} \cdot 0 + \underbrace{A \cdot \overline{B \cdot C}}_{I_5} + \underbrace{\overline{A \cdot B \cdot C}}_{I_6} + \underbrace{A \cdot B \cdot C}_{I_7} \cdot 0$$

Digital Circuits Laboratory

# LAB no. 6.

The function implementation can be done like below:

Figure 5

# 4. Lab works

Complete the following sheet according to the indications.

Digital Circuits Laboratory *LAB no. 6*.

# LAB SHEET

1. Make the 2 :1 multiplexer schematic in MaxPlus II (figure 2). Simulate it and draw the output waveform on the grid below. Compare the resulted data with the truth table.

| А              |  |      |      |      |  |

|----------------|--|------|------|------|--|

| I <sub>0</sub> |  |      |      |      |  |

| I <sub>1</sub> |  |      | <br> |      |  |

| Y              |  | <br> | <br> | <br> |  |

2. Make the 4:1 multiplexer in MaxPlusII (figure 4). Simulate and draw the output waveform  $\overline{E} = 0$ . Find the delay time and mark the logic values on the waveforms. Compare the results with the truth table.

| Е                                                                         |        |   |    |   |          |          |     |   | <br>           |            |           |          |     |   |   |     |   |           | <br> |   |       |            |            |          |            |         |      |

|---------------------------------------------------------------------------|--------|---|----|---|----------|----------|-----|---|----------------|------------|-----------|----------|-----|---|---|-----|---|-----------|------|---|-------|------------|------------|----------|------------|---------|------|

| $A_0$                                                                     |        |   |    |   |          |          |     |   | <br>¦          | ¦          | ¦         | <u></u>  |     |   | ; |     |   |           |      |   | <br>  |            |            |          |            |         |      |

| $A_1$                                                                     | !<br>! |   |    |   |          |          |     |   | <br>/<br> <br> | /<br> <br> | <br> <br> | <br>     | · ' |   |   |     | 1 | <br> <br> |      |   | <br>  | /<br> <br> | /<br> <br> |          | !<br> <br> |         |      |

| I <sub>0</sub>                                                            |        |   | Ĺ  | Ľ | <u> </u> | Ĺ        |     |   |                |            |           | İ        |     |   |   |     |   |           |      |   |       |            |            | <u> </u> |            |         |      |

| $I_1$                                                                     |        |   |    | Ĺ |          | <b>İ</b> |     |   |                |            |           | <u> </u> |     |   |   |     |   |           |      | İ |       |            |            |          | İ          |         |      |

| $I_2$                                                                     |        |   |    |   |          |          |     |   | <br>/<br> <br> | /<br> <br> |           | <u>.</u> |     |   |   |     |   | · ·       |      |   | <br>  | /<br> <br> | /          |          | <b> </b>   |         |      |

| I <sub>3</sub>                                                            |        |   |    |   |          |          |     |   | <br>           |            |           |          |     |   |   | · i |   | <br>-     | <br> |   |       |            |            |          |            |         | <br> |

| Y                                                                         |        |   |    |   |          | <br>     |     |   | <br>           |            |           |          |     |   |   |     |   |           | <br> |   |       |            |            |          |            |         |      |

|                                                                           |        |   |    |   |          |          |     |   |                |            |           |          |     |   |   |     |   |           |      |   |       |            |            |          |            |         |      |

| Б                                                                         |        |   | ·; |   |          |          | 3   | 3 | <br>           |            |           | ;        |     | ; | ; | ;   | ; |           | <br> |   | <br>  | ;          | :          |          |            | <u></u> | <br> |

|                                                                           |        | - | ·  |   |          |          |     |   | <br>           |            | <br>      | <br>     |     |   |   |     |   |           |      |   | <br>_ | <br>       | <br>       |          |            |         |      |

| A <sub>0</sub>                                                            |        |   |    |   |          |          | · · |   | <br>           |            |           |          |     |   |   |     |   |           |      |   | <br>  |            |            |          |            |         |      |

| $egin{array}{c} A_0 \ A_1 \end{array}$                                    |        | - |    |   |          |          |     |   | <br>           |            |           |          |     |   |   |     |   |           | <br> |   | <br>  |            |            |          |            |         |      |

| $\begin{array}{c} \mathbf{A}_0\\ \mathbf{A}_1\\ \mathbf{I}_0 \end{array}$ |        |   |    |   |          |          |     |   | <br>           |            |           | ,<br>,   |     |   |   |     |   |           |      |   |       |            |            | · · · ·  |            |         |      |

| $egin{array}{c} A_0 \ A_1 \ I_0 \end{array}$                              |        |   |    |   |          |          |     |   | <br>           |            |           |          |     |   |   |     |   |           |      |   | <br>  |            |            |          |            |         |      |

| $\begin{array}{c} \mathbf{A}_0\\ \mathbf{A}_1\\ \mathbf{I}_0 \end{array}$ |        |   |    |   |          |          |     |   | <br>           |            |           |          |     |   |   |     |   |           |      |   |       |            |            |          |            |         |      |

| $\begin{array}{c} A_0\\ A_1\\ I_0\\ I_1\\ I_2\\ I\end{array}$             |        |   |    |   |          |          |     |   | <br>           |            |           |          |     |   |   |     |   |           |      |   |       |            |            |          |            |         |      |